Анализ повреждений после 1000 термальных циклов

Был проведен поперечный разрез компонентов после 1000 циклов. Незначительные трещины были обнаружены на некоторых ВТС компонентах. Обычно трещины начинались на краю компонента на его боковой стороне. На месте образования пустот трещин не было.

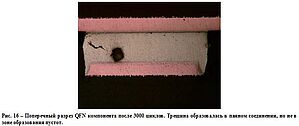

Анализ повреждений после 3000 термальных циклов

Тестирование термальным циклом было завершено после 3000 циклов. У последовательно соединенных компонентов после 3000 циклов не были обнаружены никакие повреждения. Трещины были более выражены у определенных ВТС компонентов, таких как QFN132, QFN52, QFN3550 и LGA1837. Большинство трещин было обнаружено на боку компонента (Рис.14 и Рис.15). были также замечены некоторые трещины в середине паяного соединения (Рис.16).

Большинство трещин и наиболее серьезные трещины образовались на сигнальных выводах QFN компонентов или когда было большое несоответствие в дизайне площадки компонента.

Термальные площадки компонентов QFN и многих LGA с большими размерами площадок не имели значительных трещин после 3000 циклов.

Выводы по тестированию термальным циклом

Корреляция между количеством пустот на термальной площадке ВТС компонента и надежностью его паяного соединения не была обнаружена. Трещины не шли от пустот. Не было обнаружено достаточно доказательств того, что пустоты на термальных площадках усиливают образование трещин в паяных соединениях.

Тепловое моделирование BTC

В данном исследовании мы оценивали влияние пустот в припое в термальной площадке ВТС компонентов. Экспериментальная часть была выполнена путем создания модели ВТС и использования теплового симулятора для оценки теплоотдачи в окружающую среду и печатную плату. Модель включает в себя все отдельные элементы ВТС, такие как материал корпуса, медная рамка площадки, бессвинцовый припой, печатная плата и медные дорожки. Также включены кремниевые кристаллы с информацией об измерениях и рассеивании мощности. После оценки модели путем сравнения результатов с термальным поведением, определенным поставщиком компонентов, были созданы несколько условий для образования пустот от 0% до 98% пустот путем изменения термального сопротивления припоя, основанного на олове, и прочтения поверхностной температуры на корпусе. Были также созданы дополнительные сценарии путем изменения рассеивания мощности в корпусе и фиксации результатов.

Выбор компонентов

Для термической симуляции мы использовали DC до DC регулятор QFN IR3837. Этот чип включает PWM контроллер и два Mosfets (контрольный и синхронный FET). Это устройство может функционировать при различном токе и показывать значительное рассеивание мощности, что упрощает анализ влияния пустот в припое.

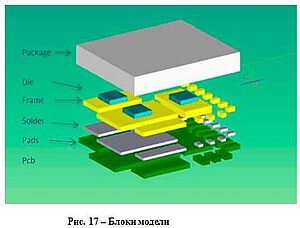

Разработка модели

Все детали корпуса были сконструированы с первичными блоками, доступными в симуляторе; с такими свойствами как геометрия, тип материала, теплопроводность и рассеивание мощности, свойственные каждой детали, и объединены все вместе как показано на Рис. 17 и Рис.18.

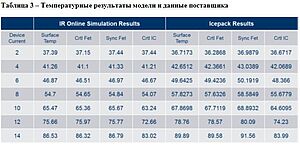

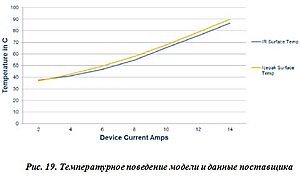

Проверка модели

Проверка модели была выполнена путем сравнения термального поведения модели с информацией, предоставленной поставщиком, что отображено в Таблице 3. Анализ включал рассеивание мощности при различных токах и показал индекс корреляции в 99%, что показано на Рис.19.

Оценка сценариев образования пустот

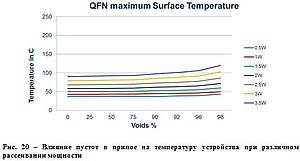

С хорошей моделью, которая почти точно совпадает с результатами, предоставленными поставщиком устройства, следующий шаг – это оценка сценариев образования пустот от 0% пустот до 98% пустот и измерение температуры на поверхности устройства при рассеивании мощности от 0,5 до 3,5 Вт. Результаты показаны на Рис.20.

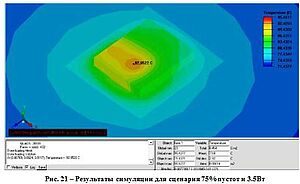

Эти результаты показывают, что количество пустот оказывает минимальное влияние на температуру, достигаемую продуктом. Рис.21 показывает результаты симулятора при сценарии в 75% пустот и 3,5 Вт.

Максимальная температура, достигнутая на поверхности устройства, составляет около 92° C. Внутренние кристаллы полупроводника показывали максимальную температуру 95.4C для синхронного FET и 91.9° C для контрольного FET. Контрольная ИС показала 84.3° C. Несмотря на то, что количество пустот на термальной площадке составляло 75%, устройство рассеивало 3,5 Вт при том, что температура полупроводника вполне отвечала спецификации устройства.

Выводы по температурному исследованию

С помощью тепловой симуляции стало возможным создать и проанализировать условия образования пустот в корпусе ВТС, что достаточно сложно выполнить экспериментально. Полученные данные показывают, что пустоты в паяных соединениях не оказывают значительного влияния на увеличение температуры устройства, так как остальные элементы в корпусе также помогают выводить образовавшееся тепло. Из полученной информации можно сделать вывод, что до 50% пустот в припое на термальной площадке является допустимым количеством для устройств с рассеиванием мощности до 3 Вт.

Заключение

Наше исследование показало, что пустоты не вызывают образование трещин в паяных соединениях ВТС компонентов во время тестирования термальным циклом от 0° C до 100° C. Данные не показали, что пустоты увеличивают риск повреждения паяного соединения. Паяные соединения маленьких сигнальных выводов обычно имеют более значительные трещины и будут повреждены в первую очередь. Термальные площадки обычно имеют больше пустот, но трещин было обнаружено меньше при 3000 термальных циклах. Исследование с тепловым моделированием показало, что пустоты не оказывают значительного влияния на увеличение температуры устройства с рассеиванием мощности в районе 3 Вт. Дальнейший анализ будет выполнен для оценки теплового поведения других конфигураций ВТС компонентов и попытки сравнить его с известной производительностью реальных компонентов.

Благодарности

Авторы выражают благодарность Raymond Tran, Quang Phung и компании Milpitas PIC Team за их помощь в монтаже. Особая благодарность Manuel Haro и Jorge Alberto Aguilar за их помощь в исследовании надежности. Также благодарим Jorge Alberto Aguilar, Tu Tran и Teresita Villavert за помощь в анализе повреждений и фотографий поперечных разрезов.

Ссылки

1. Jennifer Nguyen, David Geiger and Dongkai Shangguan, Ph. D, "Assembly Challenges of Bottom Terminated Components," Proceeding of APEX2012, San Diego, CA, 2012.

2. Jennifer Nguyen, David Geiger and Murad Kurwa "Voiding Mitigation of Bottom Terminated Components," Proceeding ofSMTAI'13, 2013.

3. IPC-7093 standard, "Design and Assembly Process Implementation for Bottom Termination SMT Components," March

2011.

4. Z. Feng, Ph.D., H. Le, R. Chung, R. Tran, S. Johal, and M. Kurwa, "How To Resolve Defects Related to Pad Design With the Aid of Non-Destructive and Destructive Methods", Proceeding ofSMTAI'13, 2009.

Источник: www.circuitinsight.com