Одна из тенденций в современной электронике – увеличение степени интеграции полупроводниковых электронных компонентов с одновременным уменьшением их физических размеров. Это стремление к миниатюризации электронных компонентов вынуждают производителей современных микросхем использовать корпуса с большой плотностью расположения выводов на поверхности микросхем.

Например, корпуса с матричным расположением выводов BGA (Ball grid array). Такое решение является компромиссом между возможностью обеспечить высокую плотность выводов на поверхности микросхемы и надежностью [1]. Сегодня в России опыт монтажа ИС в корпусах BGA имеют многие компании. При эксплуатации электронных блоков в обычных условиях, монтаж BGA и выполнение гарантийных обязательств по надежности паяных соединений особых сложностей не вызывает. Если же изделия используются в сложных условиях, то на первый план выходит необходимость обеспечения надежности паяных соединений в процессе работы изделия. Особенно проблематично это сделать из-за конструктивных особенностей данного типа корпуса ИС. Наличие бессвинцовых выводов надежности паяным соединениям так же не добавляет. Достаточно часто разработчики не имеют возможности выбора между BGA и более надежными корпусами ИС с точки зрения механической прочности паяных соединений. Именно о таком случае пойдет речь в этой статье.

Специалисты ОАО "НПО ИТ" обратилось к нам с просьбой произвести монтаж нескольких электронных блоков, на каждом из которых располагалось по две микросхемы в корпусе BGA (ALTERA MAXII, 324 вывода). По нынешним временам – задача тривиальная для многих компании, за исключением одного момента: электронный блок должен сохранять работоспособность при виброударах в осевом и радиальном направлениях с ускорением до 100 g. Разработчик имел возможность использовать микросхемы только в корпусе BGA. Задача снижения вибрационной нагрузки на электронный блок в целом решалась использованием стандартного в такой ситуации конструкторского решения – был разработан корпус с учетом условий эксплуатации изделия.

Очевидно, что обеспечить гарантированно высокую надежность паяных соединений BGA в этом случае невозможно. Нашим решением для обеспечения механической прочности паяных соединений BGA, при таких условиях эксплуатации, стало использование материала типа Underfill [2].

Материалы этого типа давно применяются для обеспечения надежности электронных блоков с BGA, используемых в различных областях электроники (от мобильных телефонов до оборонных применений). Помимо этой решается еще несколько задач. Одна из них – обеспечение герметичности BGA, т.е. пространство между поверхностью печатной платы и подложкой микросхемы. Вторая – согласование коэффициентов температурного расширения печатной платы и конструктивных элементов микросхем.

Как известно, существует несколько типов материала Underfill [2]. Помимо принципиальных различий в технологии нанесения Underfill существует разделение материалов на неремонтопригодные и ремонтопригодные. Мы остановили свой выбор на материалах второго типа. Этот выбор был сделан по нескольким причинам:

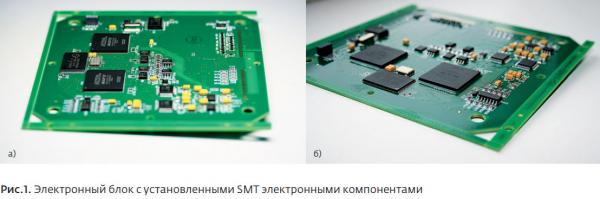

- Во-первых, Underfill наносится после монтажа микросхем (рис.1), что позволяет произвести контроль качества монтажа микросхем (визуальный, рентгеновский и функциональный) до его нанесения.

- Во-вторых, есть возможность произвести замену микросхемы в случае необходимости с повторным нанесением материала.

- В-третьих, материалы данного типа допускают нанесение Underfill после использования паяльных паст, не требующих отмывки флюса после пайки (в некоторых ситуациях данное обстоятельство может быть полезно).

Рис. 1 Электронный блок с установленными SMT электронными компонентами (нажмите на изображение для увеличения).

После проведенного анализа был выбран Underfill FF35 компании AIM. Помимо преимуществ, указанных выше, данный материал имеет приемлемые срок и условия хранения. Процесс нанесения материала разделен на два этапа: нанесение и отверждение (полимеризация). На первом этапе Underfill заполняет пространство между подложкой микросхемы и поверхностью печатной платы (рис.2) [3].

Для нанесения Underfill применялись цифровые дозаторы, обеспечивающие приемлемые производительность и повторяемость процесса. На этапе отверждения электронный блок с нанесенным материалом выдерживается при температуре 150°C в течение 5 мин. В зависимости от особенностей электронного блока параметры температурного воздействия могут быть изменены. Например, темпера-тура может составлять 100?C, но при этом время процесса увеличивается.

При нанесении Underfill необходимо уделить особое внимание схеме дозирования материала, так как от выбранной схемы движения иглы дозатора вдоль корпуса микросхемы и объема дозируемого материала зависит уровень дефектов нанесения материала. Основными дефектами при нанесении можно считать возникновение пустот, ореолов вокруг выводов BGA. Так же могут возникать отслоение и растрескивание underfill после отверждения материала [1].

После отверждения пустоты и ореолы обнаружить достаточно трудно, так как правило, они сконцентрированы ближе к центру корпуса компонента.

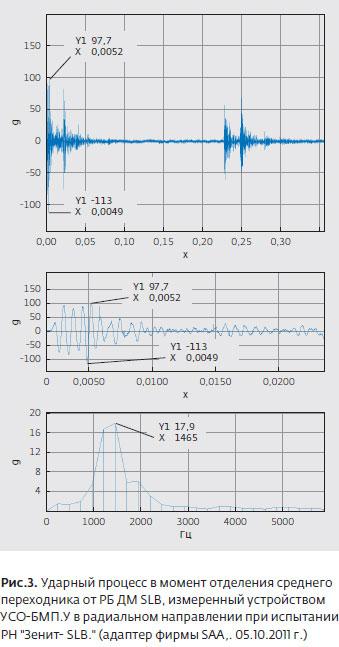

В качестве удачного примера использования Underfill, можно привести изделие ОАО "Научно- производственное объединение измерительной техники" – бортовое устройство сбора и обработки быстроменяющихся параметров процессов при исследовании ударных процессов (УСО-БМП.У) БЫ3.031.113. Это устройство используется для сбора информации телеметрических систем, устанавливаемых на разгонных блоках. Устройство УСО-БМП.У предназначено для построения систем измерения, сбора и обработки ударных процессов. В ходе проведенных испытаний и последующей эксплуатации изделие выдержало ускорение 97.7g (рис.3).

В качестве удачного примера использования Underfill, можно привести изделие ОАО "Научно- производственное объединение измерительной техники" – бортовое устройство сбора и обработки быстроменяющихся параметров процессов при исследовании ударных процессов (УСО-БМП.У) БЫ3.031.113. Это устройство используется для сбора информации телеметрических систем, устанавливаемых на разгонных блоках. Устройство УСО-БМП.У предназначено для построения систем измерения, сбора и обработки ударных процессов. В ходе проведенных испытаний и последующей эксплуатации изделие выдержало ускорение 97.7g (рис.3).

Применение Underfill в качестве решения для обеспечения механической прочности паяных соединений выводов ИС в корпусах BGA дало хорошие результаты. Об этом свидетельствует опыт использования изделий нашего заказчика в сложных условиях. Решение это не является 100%-ным, но в сочетании с другими мерами по снижению вибрационной нагрузки на электронные блоки (грамотно разработанный корпус, правильно расположенные электронные компоненты на печатной плате и т.д.) позволяет получить высокие результаты.

Литература

- Нинг-Чен Ли. Технология пайки оплавлением, поиск и устранение дефектов: поверхностный монтаж, BGA, CSP и flip chip технологии. – М.: ИД "Тех¬нологии", 2006.

- Поверхностный монтаж, № 11–12 (74), 2008.

- Поверхностный монтаж, № 1 (75), 2009.