В конце прошлого десятилетия в иностранной прессе было опубликовано сразу несколько статей о новой технологии монтажа микросхем PoP (Package-On-Package, т.е. корпус на корпус) [1,2]. Суть технологии Package-On-Package заключается в установке нескольких корпусов микросхем друг на друга. Корпус микросхемы первого уровня имеет шариковые выводы (аналог корпуса BGA) и отличается от обычных BGA только наличием контактных площадок на верхней поверхности корпуса микросхемы. Микросхема второго уровня выполняется в обычном корпусе BGA. При монтаже микросхемы устанавливаются последовательно друг на друга в 2, 3, 4 яруса. Практически сразу после появления первых публикаций на эту тему несколько наших клиентов, заинтересовавшихся этой технологией, обратились к нам с просьбой дать комментарии о возможности монтажа микросхем по этой технологии. В то время интерес к этой технологии был вызван скорее любопытством, чем реальной необходимостью. Изучив имеющиеся материалы, мы пришли к выводу, что монтаж нашими силами принципиально возможен. В начале этого года один из наших заказчиков принял решение о применении микросхем данного типа в своих изделиях, перейдя тем самым из плоскости теоретических рассуждений на эту тему в область практических.

Для того чтобы выяснить возможности нашего производства при выполнении данного вида работ, отработать технологический процесс монтажа, выявить особенности установки, пайки и контроля, нам самим предстояло перейти от теории к практике. С этой целью наши технические специалисты совместно со специалистами отдела главного технолога разработали тестовые платы .

Базовый материал- FR-4, финишное покрытие – иммерсионное золото. В конструкцию платы были введены полигоны различного типа (со сплошным заполнением и заполнением типа «сетка» - см. фото 2а, 2б), с различной степенью перекрытия зоны установки микросхемы (рис. 3а, 3б), расположенные со стороны противоположной стороне пайки.

Рис. 2 а,б. Полигоны различного типа - со сплошным заполнением и заполнением типа "сетка".

Рис. 3 а,б. Различные степени перекрытия зоны установки микросхемы.

Полигоны были введены для определения степени их влияния на качество паяных соединений.

Для проведения тестовых паек были выбраны «тренировочные» микросхемы (далее МС) компании ALKOR, являющиеся массогабаритной копией МС производимых радиоэлектронной промышленностью (см. фото 4а, 4б) и предназначенные, в том числе, для отладки термопрофилей пайки.

а)

а)

б)

б)

Рис. 4. а, б.

Существует несколько вариантов монтажа МС по технологии РОР:

- Нанесение паяльной пасты на печатную плату (далее ПП), установка МС 1-го уровня, погружение выводов микросхемы 2-го уровня во флюс (для этих целей используется специальный DIP модуль, расположенный на установщике SMD компонентов), установка микросхемы 2-го уровня, пайка;

- Нанесение паяльной пасты на печатную плату (далее ПП), установка МС 1-го уровня, погружение выводов микросхемы 2-го уровня в паяльную пасту (используется модуль, аналогичный модулю вар. 1 для данной операции), установка микросхемы 2-го уровня, пайка;

- Разновидность варианта №2, в котором паяльная паста на МС 1-го уровня, перед установкой микросхемы 2-го уровня, наносится с применением каплеструйной технологии.

Каждый из методов имеет свои преимущества и недостатки. Выбор метода для решения каждой конкретной задачи зависит от множества факторов: наличия необходимого оборудования, объёма работ и скорости их выполнения, конструктива изделия и т.д.

Нами был выбран первый метод, т.к. этот метод оказался самым простым в реализации для нас. Конструкция МС 1-го уровня, которые мы использовали для тестов, позволяли не применять паяльную пасту для пайки МС 2-го уровня. МС 1-го уровня вместо контактных площадок в верхней части корпуса имеет шариковые выводы (см. рис. 5).

Рис. 5.

При этом паяные соединения получаются достаточно надёжными и без использования паяльной пасты. Так же для отработки тех. процесса использовался вариант последовательной пайки: нанесение паяльной пасты, установка МС 1-го уровня, пайка, нанесение флюса, установка МС 2-го уровня, пайка.

Следует отметить, что автоматические установщики SMD компонентов должны иметь функциональную возможность установки МС на МС. Т.к. установка МС 2-го уровня производится на высоту, отличную от нулевого значения (поверхность ПП+ высота МС 1-го уровня).

С целью сравнения технологий оплавления, пайка производилась в конвекционной печи REHM VX3850 (без применения азота) и парофазной печи Ascon VP800.

Монтаж микросхем по технологии РoР производился на оборудовании:

- Принтер трафаретной печати EKRA E1

- Установщик SMD компонентов Siemens Siplace CF

- Печь оплавления конвекционная REHM VX3850 (11 зон нагрева верх/низ)

- Печь парофазная Ascon VP800 с вакуумной зоной

- Установка рентген-контроля Yxlon Y.Cheetah CT

- Система струйной отмывки Riebesam 23-ОЗТ

- Стереомикроскоп Vision Engineering Lynx Stereo x40

- Термопрофайлер

- Для монтажа использовались паяльные материалы:

- Паяльная паста Indium NC-SMQ-92H

- Флюс Indium

В результате проведённой работы не удалось обнаружить зависимости от типа и степени перекрытия полигонами зоны пайки на качество паяных соединений. В обоих случаях (парофазная пайка и конвекция) корпуса МС располагались параллельно поверхности платы (без наклона в какую-либо сторону). Паяные соединения имели однородный вид.

Влияние количества циклов пайки (1 или 2) на качество паяных соединений не обнаружено. Наличие второго цикла пайки (при монтаже микросхемы 2-го уровня) не приводило к появлению дефектов паяных соединений 1-го уровня.

Использование флюса для пайки МС 2-го яруса не оказало негативного влияния на качество паяных соединений.

Были обнаружены некоторые зависимости от используемой технологии оплавления:

1. При использовании конвекционной пайки было отмечено большее количество пустот в паяных соединениях, чем при парофазной пайке. Возможно, сказалось отсутствие азота в зоне пайки, на влияние которого на качество паяных соединений указывалось [4].

2. Подбор термопрофиля при конвекционной пайке потребовал большего внимания, чем при использовании парофазной пайки. Многоуровневая конструкция обладает большей теплоёмкостью по сравнению с обыкновенными МС в BGA корпусах. При сравнении со стандартными профилями для пайки BGA, используемыми для этой печи, время нахождения электронного блока в пиковой зоне увеличилось. При этом существенных изменений в профиле пайки в парофазной печи замечено не было.

3. Обнаружено влияние наличия вакуумной зоны в парофазной печи на зазор между МС 1-го и 2-го уровней. При использовании вакуума зазор практически исчезал, при этом благодаря конструкции выводов микросхемы 1-го уровня коротких замыканий между выводами не возникает.

Было отмечено наличие коробления МС 1-го и 2-го уровня в результате пайки. О явлении коробления и возможных причинах указывается во многих источниках [5, 6]. Одной из причин его возникновения может стать неоптимальный термопрофиль печи оплавления, приводящий к короблению корпусов МС на пиковых и близких к ним температурах.

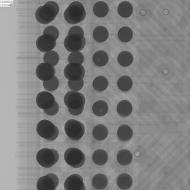

Проведение рентген-контроля затруднено ввиду особенностей конструкции PoP – изображение выводов МС, расположенных друг над другом, перекрывают друг друга (см. фото 7а, 7б).

Рис. 7а. Рентгенограмма под углом 90 град. к плоскости печатной платы.

Рис. 7б. Рентгенограмма под углом 45 град. к плоскости печатной платы.

Для проведения рентген контроля необходимо, чтобы установка рентген-контроля обеспечивала возможность проведения контроля под углом 25-50 градусов к горизонтальной плоскости печатной платы [7].

Проведение визуального контроля крайне затруднено. Ситуация аналогична проведению визуального контроля для обыкновенных МС в BGA корпусах. Контроль паяных соединений 2-го уровня осложнён наличием зазора между корпусами МС меньшего, чем зазор между ПП и МС 1-го уровня.

Несмотря на наличие особенностей монтажа МС в исполнении РoР, их качественный монтаж на ПП возможен. Одними из важных условий при этом будут наличие современного оборудования для монтажа и использование современных паяльных материалов. Не затронутой в статье осталась отдельная и очень важная задача, оказывающая не меньшее влияние на успех в выполнении монтажа, чем наличие оборудования, – это правильная разработка конструкции ПП. Микросхемы в исполнении РОР имеют маленький шаг выводов 0.5 – 0.4 мм. При этом ошибки в выборе диаметров контактных площадок, методе вскрытия паяльной маски над контактными площадками, расположении электронных компонентов на печатной плате и другие факторы, связанные с конструированием изделия, несомненно окажут негативное влияние на качество монтажа микросхем в формате Package-on-Package и надёжность работы изделия.

Список литературы:

- Package-on-Package: The Story Behind This Industry Hit (Semiconductor International, 6/1/2007).

- "POP" Goes the Future (Assembly Magazine, 9/30/2008).

- Global SMT&Packaging, 9/2009, “POP and vapor phase technology”.

- Texas Instruments, 4/2008, “PCB Assembly Guidelines for 0.4 mm Package-On-Package (PoP) Packages, Part II”.

- Amkor Technology, “A Study on Package Stacking Process for Package-on-Package (PoP)”.

- Kazuo Ishibashi, Nokia Japan Co., Ltd, 2007, “PoP (Package-on-Package) Stacking Yield Loss study”.

- Bob Willis, “The challenges of package on package (POP) devices during assembly and inspection”, 2009.