Практическое руководство по проектированию высокоскоростных печатных плат и систем. Часть 2

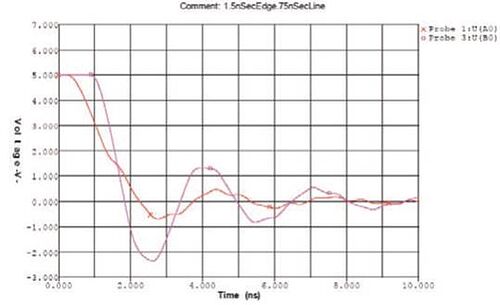

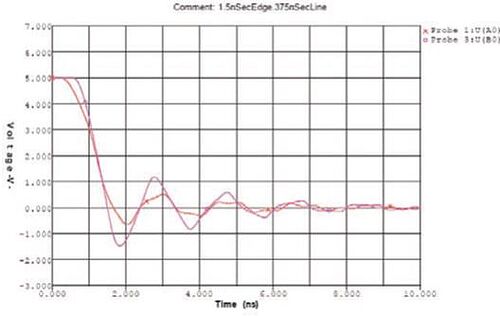

В итоге при длине в ¼ TEL амплитуда отражений по нагрузке была сокращена с -2,4 вольт до -1,4 вольт. Наконец, линия стала достаточно короткой, чтобы можно было забыть о проблемах целостности сигнала из-за отражений. Энергия, вызывающая нарушения, варьируется от -0,7 вольт до -1,4 вольт. Для схема ЭСЛ это не так. Длина линии менее 1,4 TEL может считаться пограничной между низкоскоростным и высокоскоростным проектом.

Теперь, когда граница между низкой и высокой скоростью установлена, это можно перевести в правило длины с целью установки, когда правила линии трансмиссии должны применяться к линии. Линии меньше, чем эта длина, можно отнести к категории «не важно». С линиями длиннее, чем эта длина, надо работать с использованием правил целостности сигнала. В примере – TEL составляет 1,5 наносекунды. ¼ от этого – 375 пикосекунды. В большинстве печатных плат сигналы проходят примерно 6 дюймов за одну наносекунду. Соответственно, для фронта в 1,5 наносекунду линии, длиннее 2,25 дюймов потребует контроля импеданса и некоторой формы управления отражениями.

Таблица 19.1 приводит несколько стандартных логических семейств с их временем нарастания и TEL. Используемые сейчас логические семейства все имеют время нарастания и спада 0,5 наносекунд или меньше. Даже логические части, предназначенные для общего использования, имеют такие показатели. Это объясняется постоянным сокращением размеров транзисторов, которые составляют эти логические части. В результате этих еще более быстрых перепадов, длина линии трансмиссии, при которой линия может считаться «высокоскоростной», становится все меньше и меньше. Таблица 19.1 показывает эти данные для времени нарастания и спада в пределах от 1 наносекунды до ¼ наносекунды.

Из данных в Таблице 19.1 очевидно, что виртуально каждый сигнал в большинстве сегодняшних печатных плат имеет потенциал быть нарушенным из-за выброса напряжения. Данное отношение TEL к времени нарастания и спада является первичным фактором определения необходимости контроля импеданса.

Каждый путь сигнала длиннее, чем ¼ ⁄4 TEL, имеет потенциал к нарушению из-за избытка напряжения. Это первый тест для определения того, когда разработка становится высокоскоростной.